Master in Artificial Intelligence (UPC-URV-UB)

**Master of Science Thesis**

# PARALLEL ERROR-CORRECTING OUTPUT CODES CLASSIFICATION IN VOLUME VISUALIZATION: parallelism for IA and IA for parallelism

Oscar Amoros Huguet

Advisor/s: Sergio Escalera, Anna Puig Dr./Drs. on behalf of the Advisor/s: Sergio Escalera, Anna Puig

### UNIVERSITAT DE BARCELONA, UNIVERSITAT POLITECNICA DE CATALUNYA, UNIVERSITAT ROVIRA I VIRGILI

## Abstract

Facultat de Matemtiques UB Departament de Matemtica Aplicada i Anlisi

Master in Artificial Intelligence

by Oscar Amoros Huguet

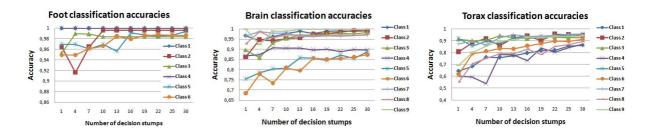

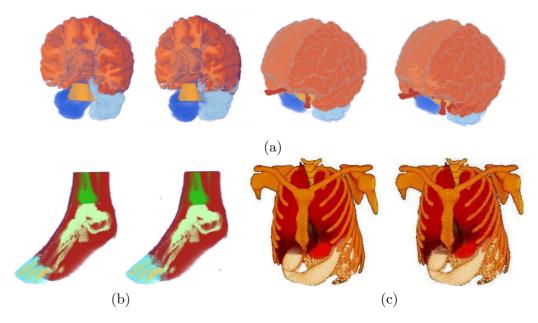

In volume visualization, the definition of the regions of interest is inherently an iterative trial-and-error process finding out the best parameters to classify and render the final image. Generally, the user requires a lot of expertise to analyze and edit these parameters through multi-dimensional transfer functions. In this thesis, we present a framework of methods to label on-demand multiple regions of interest. The methods selected are a combination of 1vs1 Adaboost binary classifiers and an ECOC framework to combine binary results to generate a multi-class result. On a first step, Adaboost is used to train a set of 1vs1 binary classifiers, with a labeled subset of points on the target volume. On a second step, an ECOC framework is used to combine the Adaboost classifiers and classify the rest of the volume, assigning a label to each point among multiple possible labels. The labels have to be introduced by an expert on the target volume, and this labels have to be a small subset of all the points on the volume we want to classify. That way, we require a small effort to the expert. But this requires an interactive process where the classification results are obtained in real or near real-time. That why on this master thesis we implemented the classification step in OpenCL, to exploit the parallelism in modern GPU. We provide experimental results for both accuracy on classification and execution time speedup, comparing GPU to single and multi-core CPU. Along with this work we will present some work derived from the use of OpenCL for the experiments, that we shared in OpenSource through Google code, and some abstraction on the parallelization process for any algorithm. Also, we will comment on future work and present some conclusions as the final sections of this document.

## Chapter 1

## Introduction

In this chapter we present a summary of the goals and contributions of the thesis.

### 1.1 Goals

The main and primary goal of this thesis has been to explore the interaction of AI and parallelism. How can AI algorithms be parallelized, and how much do they benefit from that, as well as have a look on what can some AI technologies add to the design of parallel computing systems.

Our main goal in this thesis is to have a working proof of concept of a classification framework for medical volume dataset, that has to be interactive and semi automatic. To accomplish this, we want to implement a multi classification functionality, use standard visualization tools, and achieve accuracy and interactivity constraints. For matching the interactivity constraint we use parallelism.

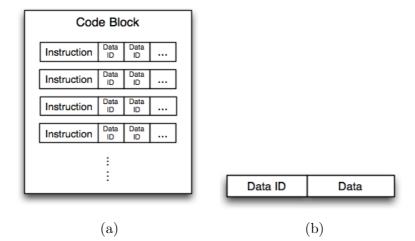

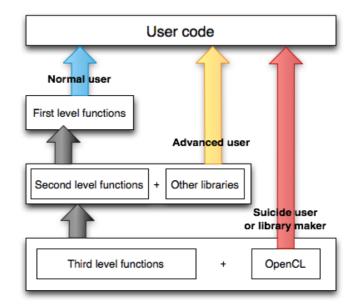

Other goals have been appearing during the development of the thesis, like the creation of AIMparallel, a methodology for easing and guiding the parallelization process of an algorithm and SimpleOpenCL, a framework we created, devoted to reduce the amount of code needed in order to create a parallel OpenCL program.

As a second main goal, to explore AI techniques that could help on solve some problems on parallel computing designs, we found Multi Agent Systems is a source of a lot of features desirable for parallel computing systems of the future. So we propose a system based on specifically Self Organizing Multi Agent Systems.

This project requires knowledge from a wide variety of fields. Computer Vision, Machine learning, Computer Science (Parallelism), Visualization and Multi Agent Systems.

### **1.2** Contributions summary

In this thesis we show two proposals. The first and main one is a classification problem, and it's implementation using parallelism. The second one is based on the experience and learning process of the first proposal. On this second proposal we show a draft of a parallel computing system based on Self Organizing Multi Agent Systems, with some basic experimentation. On the first proposal we used parallelism to implement IA techniques, and on the second one we use IA technologies to define a parallel computing system.

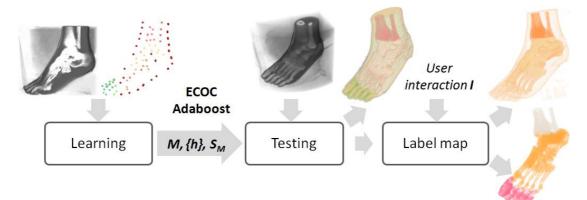

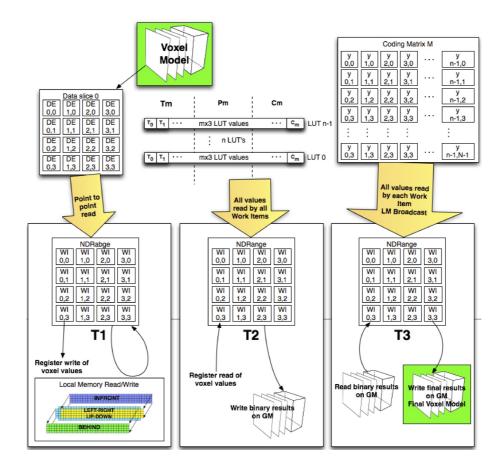

For the classification problem we propose a general framework of supervised statistical classification methods to label on-demand multiple regions of interest (see Fig. 3.1). This provides an interactive classification/segmentation generic framework that could be used in several real applications, and it can be used with any existing classification/segmentation state-of-the-art method. The framework is composed by a pre-learning stage and an on-demand testing stage included in the renderer. The learning step gets a subset of pre-classified samples to train a set of Adaboost classifiers, which are codified as TFs, and combined in an ECOC design. Each classifier encodes a set of relevant properties in a 1D texture. We deal with several properties, such as density, gradient, space location, etc. of the original data without increasing the dimensionality of the classifier. Next, the testing stage multi-classifies and labels a subset of volume classes based on user interaction. The label mapping defines clusters of the selected classes, and then it assigns optical properties and importance values to the final output classes to be visualizated. The labels computed in the testing step in the GPU memory can be used in several volume visualization approaches: to skip non-selected regions, to help computing importance values to different context structures, or to select the focus of interest for automatic view selections, just to mention a few. The label mapping reduces the edition of the TFs by only assigning the optical properties of a label. In addition, the labels, as a TF, can be applied directly to the voxels values, or alternatively to the sampling points derived from the interpolation of the nearby voxels. Up to now, the complexity of the learning process and the testing step of a large amount of data do not allow their integration into an interactive classification stage of the user-interface volume pipeline. In this sense, our proposal improves the TF specification process by combining a pre-processing learning step and a rendering integrated GPU-based testing method.

In summary, on the classification problem we bring four contributions: First, the definition of a general framework for multi-classification of volumes based on the ECOC approach; Second, the use and parallelization of Adaboost as a case study of this general framework; Third, the computation of an on-demand adaptive classification to a subset of features of interest; Finally, the proposal of a GPGPU OpenCL implementation of the testing stage of the multi-classifier integrated into the final rendering. This work serves as a proof of concept for future embedding of the training step in the visualization pipeline. In this sense, online learning will be performed on-demand in the rendering. Results on different volume data sets of the current prototype show that this novel framework exploits GPU capabilities at the same time that achieves high classification accuracy.

The parallel computing system mainly proposes a design change on parallel computing systems, based on the evolution of the technology, that allows to have extra hardware executing Agent programs for the benefit of the whole system. This benefit comes from the optimization of the network use and from the decentralization of the scheduling. Many of this benefits are already pursued on other projects for parallel computing languages and frameworks, but they continue to use traditional programming paradigms for the implementation of the system.

The rest of the thesis is organized as follows: Next chapter overviews the parallelism state of the art and presents our AIMparallel methodology. Chapter 3 presents the classification problem, it's definition, parallel implementation, experiments and results. Chapter 4 explains the SOMAS based parallel computing system proposal with a basic first definition, a basic simulator and some small experiments with it. Finally chapter 5 gives some conclusions on all the work done.

## Chapter 2

## Parallelization

### 2.1 Introduction

On this chapter we are going to introduce the problem of parallelization and more specifically parallelism on the GPU. This chapter introduces concepts necessary for the main contribution, the classification problem, and que parallel system proposal. We begin with an state of the art and ends with a parallelization methodology and nomenclature that we propose as part of this thesis.

### 2.2 State of the art

### 2.2.1 Introduction

Parallelization technologies have been widely used for applications where the amount of data and/or calculations is very high. For having results in an acceptable time on this problems, several computers are required to be computing different parts of the same problem at the same time. Many languages and very specific networking and computer technologies have been used to tackle scientific or statistical problems for both public and private science and industry along last decades. Vector units first (instruction level parallelism) and Shared Memory Multiprocessors later introduced parallelism in certain degree into workstations, allowing for a wider audience to create parallel programs, or for increasing the processor densities of clusters.

This audience broadening turned into a tendency, and many languages have been adopted as standards like OpenMP (for shared memory multiprocessor systems) and MPI (for clusters). Nevertheless, many technical problems arise almost at the same time:

• An increased cost and difficulty of shrinking processors.

- An increased cost and difficulty of keeping power consumption levels with the increase of transistor number, added to an increased demand of power efficiency for mobile devices.

- An increased cost and difficulty of keeping the data interfaces (from networks to memory interfaces and off-chip wiring) to keep the data transfer performance on pair to the processors processing capabilities.

For reducing this problems at a hardware design level, the easiest solution is to increase parallelism in several architecture levels, plus increasing power modularity on the processors, leading to many parts of the processors being turned on and off depending on usage for saving power, and matching thermal requirements.

This increase on parallelism, at the processor and ALU level has many problems:

- Parallelism is not a need by it self in many applications, but an added complexity in order to fully use new systems. Programmers tend to skip it or even don't know how to use it.

- Vector units usually need proprietary compilers to be used, and is complex.

- At multi-CPU level, cache memories intended to mitigate the memory interface performance problem became a problem. The more CPU's the more complex and big becomes the caches and memory coherency ends up consuming most of the power and chip surface.

- Parallel programming models like OpenMP or MPI are known by a small community of programmers, and businesses try to avoid their need as much as possible. A proof of this is the success of specific frameworks or languages like those based on Map-reduce [JD04], Scala [dSOG10], etc... They are specific for certain tasks or needs, but they are easier to use since they are very high level.

GPU (graphics processing units) have been very specific processors that had much more freedom to evolve than general-purpose processors like CPU, which have to manage an operating system with all the complex functionalities it implies. Additionally, GPU's are added to systems with a piece of software (a driver) that makes the systems to know how to communicate with them. Also, some GPU programming standards appeared, like OpenGL, that abstracted architectures and offered a single graphics programming model for all GPU's. All this modularity and specific functionality allowed GPU designers to create almost any architecture, that better matched the graphics computing needs. These needs are mainly programmable data parallelism for allowing the programmer to create their own visual effects, a big memory bandwidth and some very common functionalities that can be tackled with super fast fixed function units. As a result, GPU ended being a relatively cheap and very parallel and fast architecture, that once adapted with the help of some new languages (CUDA and OpenCL), evolved into a more general purpose parallel processors (GPGPU). Nevertheless, GPU's are still not true general purpose, they are very good for some tasks, good for some others, and bad for all serial codes or task parallelism (like operating systems). CPU's are the opposite, they can provide a very limited amount of parallelism compared to GPU's with a very less efficient power consumption per core, but they are much more efficient on computing serial tasks and operating systems. This makes CPU's and GPU's a pair of very complementary architectures, not to mention that they are present together in almost all computer systems, including mobile devices.

But CPU's and GPU's are not the only architectures around. In general, architectures can be classified by it's level of specificity or generality on the task they can perform. ASIC (application-specific integrated circuit) circuits designed to a single task are the most efficient solutions, but they are not adaptable, since they are not programmable, they will always perform the same task. FPGA's (Field Programmable Gate Array) are a bit more flexible, since they are intended to be programmable circuits, but programming a circuit is much more complex than programming on a compiled high level language, for a general purpose processor. GPU's include ASIC functionalities and semi general purpose highly parallel units. Some CPU's are starting to include some ASIC units for video processing too, like Intel Quick Sync. Nevertheless, mostly on mobile devices, there are more specific purpose units like video processors, and a lot of DSP that are mainly ASIC's.

Programming GPU's for general purpose can be done mainly with CUDA or OpenCL languages. They are mainly the same, and their performance too, but CUDA only works for NVIDIA GPU and OpenCL works in any GPU, CPU and is designed to work on any existent and future accelerator (floating point operations accelerator) technology like FPGA's and ASIC's. The advantages of CUDA are the availability of some NVIDIA GPU features that might not be supported in OpenCL (since NVIDIA is not creating OpenCL extensions for supporting them) and the more programmer friendly options that CUDA has on the CPU side of the code. As CUDA has been the first computing oriented GPU language to appear, it gained broad adoption on the scientific community and there are many papers on the literature implementing varied algorithms from many domains in CUDA [GLD\*08, HGLS07, NL07]. Nevertheless, this algorithm implementations are almost identical when programmed in OpenCL, and additionally, having OpenCL code allows to test a wider range of hardware, with less coding effort than using proprietary languages for each hardware. In fact it is possible to use exactly the same code for different vendors.

Given the data parallelism of the algorithms and data we are using, the natural choice is GPU's. Additionally, the data being processed is already on the GPU for visualization

so we are not creating any unnecessary data transfer. For code portability and being able to work with different architectures we chose OpenCL instead of CUDA.

On the next sections we will review some important aspects of the GPU architecture and the GPU programming model.

### 2.2.2 GPU architecture review

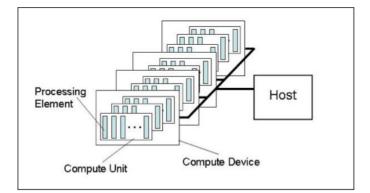

GPU's are mainly a set of big vector processors, sharing a common memory space and each one with a big control unit. This vector processors or compute units (OpenCL nomenclature) have a very varying amount of ALU's for integer and floating point operations, depending on the model and the vendor (from 2 ALU's in a super scalar pipelined fashion on Intel GPU's to 192 ALU's on NVIDIA GPU's).

On this section we will divide the explanation of GPU architecture in to memory hierarchy, execution internals, and programming model.

### 2.2.2.1 Memory hierarchy

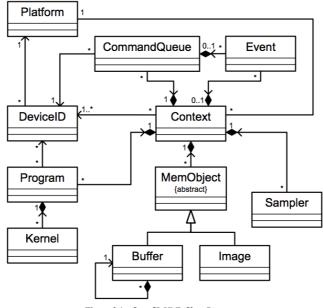

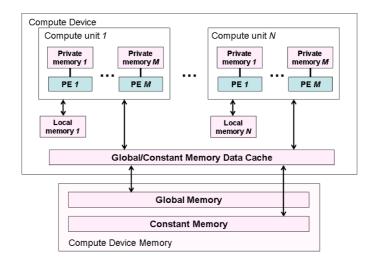

The main memory of this GPU's usually is a set of GDDR5 banks, in case of discrete PCIe GPU's. More recently, some GPU's share the same CPU DDR3 memory, where the operating system splits it into two different memory spaces, saving costs, but reducing performance. The newest technologies already available, allow the system to either simulate a single memory space for GPU and CPU, regardless of the real memory being used (NVIDIA CUDA 6), or to actually allow the GPU to coherently use the same memory space as the CPU through driver and hardware support (some AMD APU's). This memory is called global or device memory, according to OpenCL and CUDA nomenclatures respectively. From now on we will only use OpenCL nomenclature for clarity. Refer to Appendix A on this document for doubts about OpenCL nomenclature.

Additionally to this global memory, compute units usually have access to a coherent cache that allows to reduce the memory latencies generated when accessing global memory, that until today is always off-chip memory. Accessing off-chip memory implies signal amplification and sometimes translation. All this process is time and power consuming. Compute units might have to wait up to 600 computing cycles in order to have a single global memory transfer. For that reason, additionally to this cache memory, there is another memory space private to each compute unit, that is small but very fast, who's latency is usually 2 computing cycles. This memory is called local memory, and the programmer can explicitly create pointers to this memory space.

Local memory is more complicated than that though. When a programmer declares a variable that resides into local memory, there will exist as a different copy of the same variable on each compute unit. The programming model, allows the programmer to identify each one of the copies using thread id's instead of variable indexing as in standard C. We will see more about this on the Programing model section.

Finally, each compute unit has a big register bank where instructions and data reside. On modern GPU's, we can declare a variable to be private, so it will more provably reside on registers, that is the fastest memory on the GPU. Nevertheless, the scope of private memory is reduced to a single thread, so there will be a copy of this variable for each thread on each compute unit. Again, the programmer can use thread id's to know which of the copies is he using, but each thread is responsible by default of one copy and can not access directly the other thread's copies. The data has to be moved to local or global memory in order to be accessible by other threads.

### 2.2.2.2 Execution internals

Compute units execute vector instructions named warps or wavefronts that can be usually split into smaller vector instructions if it is convenient on execution time. For instance, if only the first half of the warp has the data available to execute. Compute units have a memory management unit, so they can fetch data and execute instructions at the same time. This allows for memory latency hiding.

The programming model allows to treat each one of the data elements on a vector instruction as private memory for a different thread. If on a single warp, two or more threads have to execute a different instruction on the same data, this can only lead to have two or more separated warps, each executing different actions on different data elements. This clearly reduces parallelism. So divergence inside vector instructions is allowed at the programming level, but is translated into more instructions at the hardware level.

One of the most important concepts though, is coalescense. If all the data required by a warp, exists on consecutive positions in memory, and on the same memory bank, then all this elements can be read on a single memory access. In the worst case, if every data element required by the warp resides on different memory banks, then there will be a data transfer for each element instead of one for all. Cache memories mitigate the problem of non coalescing accesses but still, it is a problem when accesses are very sparse, and the proportion of calculations per memory access is low.

### 2.2.2.3 Programming model

First of all, it is important to remark that a program that uses GPU for computation has two separated codes. The Host code and the Device code (see Appendix A). When we talk about the GPU programming model we are talking about the Device code, that is the code compiled for the GPU and executed on the GPU.

The GPU programming model stands on a basic principle. The code that the programmer writes, is executed by default by all existing threads. The number of existing threads is set up by the programmer on the Host code, so before the Device or GPU code is executed. Additionally, this threads or Work Items (as in OpenCL nomenclature) exist on a 1, 2 or 3 dimensional space. This space is called NDRange in OpenCL, where N can be 1,2 or 3, indicating the dimensionality. Then, each Work Item has id's with as many components as dimensions the space it exists in. Specifically, a Work Item is related to the following id's:

- Global id: This id is a unique id that identifies the Work Item on the NDRange space. It has 1, 2 or 3 numerical components. A Work Item in a 2DRange space has a global id of the shape (x, y).

- Local id: Work Items are grouped into Work Groups. The first dimension of the Work Group ideally should be multiple of the size of a warp. So, ideally, Work Groups are packs of several consecutive warps. They can be consecutive on any of the dimensions. See more about work groups on Appendix A. So a local id, identifies a Work Item inside the Work Group it belongs. That means that different Work Items can have the same local id, if they are in different work groups, but not if they are on the same work group. Local id's have the same shape as global id's. In the case of global id's, they are all unique.

- Group id: Work Groups also have an id for the programmer to be able to identify them. They have the same dimensionality as the NDRange.

By default, all Work Items are independent of each other, but they are executing the same code. In order to make them operate on different global or local data, we can use their id's to index pointers. That way, all Work Items will perform the same operation, but on different data. This is exactly data parallelism. But also, we can use the Work Item id's on conditional statements. That way, each Work Item can perform a different task. As we have seen previously, this leads to a reduction of overall performance.

The reason why it is possible to do Work Item divergence, despite it is bad for GPU performance, is because the alternative, moving data back to CPU (because the CPU does serial execution faster), is usually much slower than doing it directly into the GPU. This is because the time spent on moving the data can be greater than the time the GPU will spend executing serialized parts of the code. Nevertheless, this can change with the newest hardware, where GPU's have the capability to work with x86 virtual memory. In that case, there are not data transfers, only cache misses, if the GPU and CPU are not sharing the same cache.

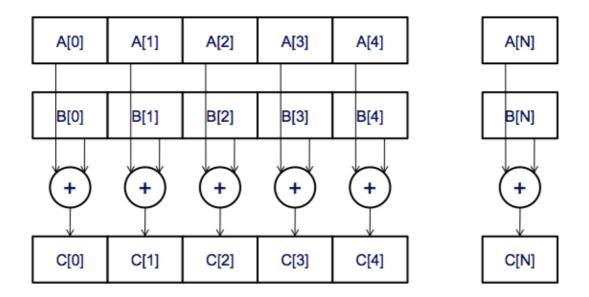

FIGURE 2.1: Vector addition in parallel of variable arrays A and B storing the result in variable array C. On an 1DRange kernel, Work Item 0 reads A[0] and B[0], adds the two read values and stores the result in C[0].

### 2.2.3 GPU programming review

GPU programming is increasingly becoming the art of finding data structures and algorithms that allow some programs that are difficult to parallelize or coalesce, to run fast on the GPU.

Some of the most basic examples are dense matrix multiplication, stencil operation on volumes, vector addition, etc... As we can see on figure 2.1, some algorithms are perfectly suited for GPU's, because each Work Item is reading a memory position that is contiguous to the memory position that the next Work Item is reading, therefore, all warps will use all ALU available (except maybe for the last warp if N in figure 2.1 is not divisible by the warp size).

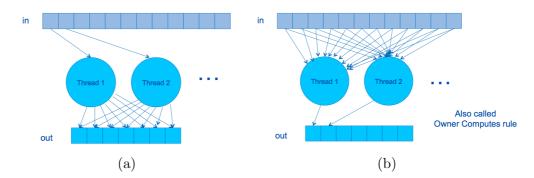

More difficult codes though present several programming difficulties to overcome, or different behaviors than in CPU. For instance, like particle simulations where scatter operations used to be more efficient on the CPU, but on GPU gather operations turn to be more efficient. We can see an illustration of this on figure 2.2. This turned to be very important to our implementation since we finally implemented the "owner computes all" rule mentioned on figure 2.2 (b). This means that conceptually we assign an output to a Work Item, and this Work Item is going to do all the work in order to obtain the output. It is not so obviously the best solution though, as we will see later.

Other algorithms are difficult to parallelize like sparse matrix. The CPU optimized sparse matrix algorithms that use data structures like CSR (Compressed Sparse Row format) [Rob] don't run very well on GPU's and there are some changes that can be

FIGURE 2.2: Scatter and gather operations. Both operations are equivalent in terms of results. (a) Scatter operation where each thread or Work Item reads a single input and writes partial results to multiple outputs. (b) Gather operation where all threads read all the input and each thread generates a single output.

done to improve performance. Other sparse matrix formats have been proven to be more efficient like a combination of ELL and COO [BG08] formats to make the algorithm to use the GPU resources as much as possible.

### 2.2.4 Conclusions

As GPU's are relatively cheap, and our algorithm is very data-parallel, we select them as the architecture with which to achieve the interactivity constraint. With the goal of having a portable code that can be deployed in any future architecture, plus being able to compare different present GPU implementations, we decided to use OpenCL in our experiments. Additionally we explored several possible OpenCL implementations to find the fastest and to better understand the GPU behavior.

### 2.3 AIMparallel Methodology

### 2.3.1 Introduction

In order for the reader to follow the implementation discussion, we first need to describe the nomenclature we will use. This nomenclature follows the definitions that the AIMparallel methodology (a methodology we created) presents. For that reason we will present AIMparallel in this section.

With AIM parallel we describe in general the problem of parallelization. Working with the algorithm implementation we have found the need for a generalization when describing the analysis of an algorithm and the relation of this analysis with the analysis of the features of the target parallel architecture. For that reason, we created a parallelization analysis methodology, not only for easing the analysis of algorithms with many possible parallel implementations, but also to more easily document and communicate this analysis.

### 2.3.2 Definition

In this section we describe the AIMparallel methodology. This methodology is provably already mentally used by many experienced parallel programming users, but we wanted to give it a name and specify it in a generic way to ease the learning curve of all the new incomers on parallel programming, as well for experienced programmers that for the first time have to deal with the fact of having to tune parallel code on different parallel systems.

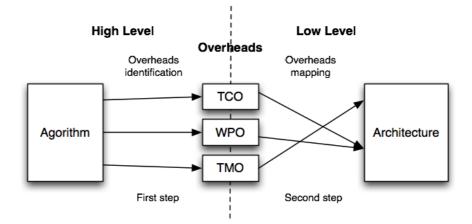

AIMparallel describes two levels of analysis, as seen in Fig.2.4. A high level that must be the first used, and a low level that needs the information extracted from the high level to be useful. On the high level AIMparallel performs an algorithm analysis on a theoretical system whit non defined resources. In this analysis we start generating parallelization options for that algorithm with the goal of not to restrict too much the options but to see how the algorithm behaves when changing granularity, and memory layouts. This behavior is specified and labelled by three main overheads that we defined (TCO,WPO,TMO), that can be treated as a value that quantifies how much of each one of those overheads each parallelization option generates. On the low level, AIMparallel maps this overheads to the specific characteristics of the programming model and architecture. This mapping gives the information of how much a certain kind of overhead does affect to the overall performance in this parallel system. It is important to note that we use the term overhead as computing cycles lost doing things related to system management or doing nothing because of lack of work balancing or paralelization.

Some of the three proposed overheads are composed of two parts. The amount of overhead produced by the algorithm behavior, and the amount of overhead produced by the system behavior and design. The system overheads could be something that vendors previously benchmark and label with standardized numbers as a reference value. That way, the programmer could skip the tedious part of understanding the inner workings of the architecture needed to infer this overheads. Nevertheless, we propose that the programmer does not exhaustively quantify this overheads (unless it is extremely necessary). In many cases we can find on vendor documentation many information about which are the weaknesses and strengths of each architecture so we can use approximated values or inequalities (greater than, smaller than), that give valuable information to the programmer.

Next we describe the three generic overheads we defined, TCO, WPO and TMO.

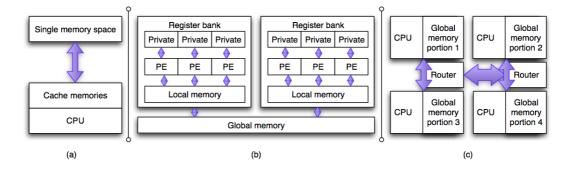

FIGURE 2.3: (a) Single memory space, (b) GPU memory hierarchy, (c) Adapteva's Epiphany network on chip memory hierarchy.

- The first overhead is called *Thread Communication Overhead* (TCO). It expresses the computing cycles lost when performing read/write operations from a thread to any of the memories of the memory hierarchy. From the algorithm side TCO it is affected by the number of memory accesses (algorithm-TCO or aTCO), and the temporal and spacial memory locality on that accesses. This is always affecting the performance on any system, so a measure of greater or lower locality on data accesses will help. On the system side it is affected by many system specificities (system-TCO or sTCO). Parallel and non parallel systems use to have a hierarchical memory system that tries to make the processors work with the low latencies of the small and fast memories, while having access to all the capacity of the higher latency, lower bandwidth big memories. As we can see on Figure 2.3 there are several memory distributions in different architectures or systems. We are also considering distributed systems, where each node has it's own memory space, and nodes communicate with messages through a network. In this case, messages have a big TCO because of both latency and bandwidth. In all the systems, processing elements are reading data from different memories, being they part o a single memory space or not. The programmer, can always manipulate the code to implicitly or explicitly modify the behavior of the accesses in order to reduce their number, so reduce TCO. sTCO then measures how bad is for a given system, that the algorithm has poor data locality, like a factor that increases more or less the aTCO depending on the system features. So, if we quantify this overheads, we could obtain a total value of TCO for a given algorithm parallelization option, and a given parallel system with a simple  $TCO = aTCO \times sTCO$ .

- The second overhead, named Wasted Parallelism Overhead (WPO), relates to the computing cycles lost when the number of working threads is smaller than the number of processors, due to the code or due to synchronization or other questions. If the number of processors of our theoretical system is unlimited, we can always say that, for a parallelization option A with less threads than another option B, option A has aWPO over B. So aWPO is a measure of the granularity

of the algorithm partition. From the system side, sWPO is a measure of how much parallelism can the system afford, either proportionally to the number of cores, or through resources that allow the system to exploit having more active threads than cores. This time, the relationship between aWPO and sWPO is not that clear. Up to a certain point it is beneficial to increase the number of threads, but given a limit (that can depend on the amount of resources used by each thread), increasing thread count can penalize performance. This behavior could be drawn on a 2D graph where y is the performance, and x is the number of threads. This is a function, and that function depends mainly on the system resources. Finding this function and taking into account the resources used per thread is a tedious work for the programmer. A more intuitive way of handling this, that is broadly used, is to read some recommendation about the number of threads that use to be good for each system. Still, we can give some useful clues to the programmer by defining sWPO as a number that reduces aWPO according to the system resources. This time then  $sWPO = \frac{1}{SR}$  where SR is a value that represents the system amount of computing resources (number of cores or vendor recommended number of threads) and aWPO = NT where NT represents the number of threads used. Then WPO follows

$$WPO = \begin{cases} \frac{1}{aWPO \times sWPO} & \text{if } NT < SR\\ aWPO \times sWPO & \text{if } NT >= SR \end{cases}$$

This formulation can be used to decide which hardware to use or which algorithm partition or parallelization techniques to use. Then extra-tuning can be done finding the right value of SR for the algorithm by testing the code and different NT values.

• Finally, the Thread Management Overhead (TMO) is related to the cycles lost when creating, destroying and scheduling threads. Again, we have algorithm and system TMO (aTMO and sTMO). Using a big number of threads, and creating a destroying a lot of them both create aTMO. Depending on the system implementation of the thread, sTMO will be higher or lower. This time, the relationship of both aTMO and sTMO is direct  $TMO = aTMO \times sTMO$ . Nevertheless sTMO can vary on some languages since scheduling policies can be different and selected by the programmer.

With this overheads and the methodology to use them, we can select where to put our effort to improve performance when parallelizing a code for an specific system, but also, we can recycle the high level analysis for considering implementations in other architectures with some work already done. Once the programmer has chosen what to improve, then he has to focus on the specific architecture, and all those characteristics that affect to the most relevant overheads found. Also, this three overheads could be used by vendors to provide very useful information about the specifics of the performance of their systems, helping customers to find the perfect fit for their needs, a not very trivial question.

FIGURE 2.4: Two step methodology for analyzing parallelization options for a given algorithm and a given parallel architecture, using the three pre-defined parallelization overheads.

### 2.3.3 Low level overheads mapping

In this section we will describe the influence of each of the three overheads on specific architectures. This step is mandatory and implies the study of the architectures being used. This could be simplified if vendors could provide some standardized numerical values for each of the three overheads, that allow to more easily compare parallelism characteristics of different systems.

### 2.3.3.1 GPU overheads mapping

On this section we will comment on the three system overheads one by one, and add some discussion at the end.

• sTCO: The use of the GPU memory hierarchy is the most sensitive aspect for obtaining a good GPU performance [KH10]. The communication between work items (threads) is done through this memory hierarchy. Therefor, on GPU's, *sTCO* is caused by big memory access latencies, and it is the programmers duty to avoid it as much as possible by properly and explicitly using the memory hierarchy. Nevertheless, latencies and bandwidth are much higher than for instance distributed systems. Despite that, once the parallelization option is selected, if a programmer wants to optimice a code for GPU he can approximate the number of cycles lost,  $N_{cl}$ , when introducing a memory access to a specific memory of the memory hierarchy. This value will be a worst case, since it doesn't take into account caches or latency hiding as in Equation 2.1.

$$N_{cl} = M_{ao} \times N_a \times C_f \tag{2.1}$$

$M_{ao}$  is an average of the cycles lost per memory access;  $N_a$  is the number of work items that perform the memory access; and  $C_f$  is the coalescing factor defined as  $\frac{1}{nWI}$ , where nWI is the maximum number of work items that can perform a memory access operation at the same time (coalesced), for that memory access.

- sWPO: on GPU's sWPO is very big since they have a lot of cores to be used, and the total amount of computing power depends on having a lot of threads working. In fact, SR > numberofcores, since for exploiting all the cores for the maximum number of cycles on a program execution, it is necessary to have much more threads than GPU cores. It is important to note that GPU threads are very different to CPU threads, since there is no OS running on the GPU, no processes or threads as data structures that identify streams of code. The threads exposed on the programming model are translated into SIMD data positions.

- sTMO: on GPU's threads don't exists as data estructures, so there is no real thread management. The consequences of uncoalesced reads and thread divergence could be considered sTMO, but they are conceptually related to both WPO and TCO. The real sTMO is the situation where the code for each thread is very big, and some of the instructions need to be on Global Memory (See Section 6.2.3). Of course, reading instructions from global memory instead of register banks is slower. Another consequence of big GPU threads is the reduction on the number of work items active on each GPU multiprocessor. This reduces memory latency hiding. Also, new technologies like NVIDIA dynamic parallelism allow to create and destroy more threads, action that has a penalty on performance. Another way to change the number of threads on a GPU program is to write different kernels with different NDRange sizes. The only way to communicate from one kernel to the other is to store the data on global memory, something slower than keeping the data on faster memories. So we know now when sTMO increases on GPU's.

We have now mapped the GPU architecture main characteristics to three concepts that we can apply to any other parallel architecture, so the generic analysis becomes useful. We will show that it is useful to categorize the performance problems, and have abstract and common terms to refer to them across different architectures to ease the parallelization analysis and discussion.

### 2.3.3.2 Overheads mapping for CPU's with OpenMP

As standard CPUs have a limited amount of cores (from 2 to 16 per chip), one of the main overheads is the WPO. For this reason, we have to reduce the number of threads to close to the number of cores, sometimes more and sometimes a bit less, depending on the runtime management and DMA's. Also, even there are fewer cores there can be WPO because of work unbalance. So we have to analyze the code behavior to determine which OpenMP for loop parallelization scheduling is better in order to avoid WPO and don't generate too much TMO. In the case of TCO, we have to think of data locality. There are no local memories on the CPU, but we can increase the cache performance by increasing the spacial and temporal data locality of the operations in the code, so we will use more times cache blocks before replacing them with different data. Instead of explicit TCO optimization like in GPU's we have an implicit optimization.

### 2.3.3.3 Overheads mapping for CPU's with GCD

GCD [App09] is an API developed by Apple based on C Blocks, that allows the programmer to forget about the computer resources, and focus only on the sequentiality or asynchronicity of each part of the code, regarding the main thread of the program.

GCD at the programmer level substitutes the threads with queues, in where we can enqueue Blocks of code that can run asynchronously with the main thread. This queues are data structures much lighter than threads, that are accessed by few system controlled threads. The threads are responsible of searching for Blocks on these queues. This minimizes TMO and WPO by parallelizing the work scheduling for balancing. As the active threads are controlled by the system, the TMO is minimized automatically without the intervention of the programmer. The programmer does not need to analyze which is the perfect number of threads for a system, because the system is managing it. In fact, GCD can be aware of the active threads for the application using blocks, in order to reduce the number of active threads for the application using blocks, in order to reduce the number of context switches, and improving overall system performance. Nevertheless, this last feature is not affecting our tests, since we tested the execution times in systems running the minimum set of idle system processes and daemons and our code.

GCD can further reduce the WPO by using two types of queues, a global concurrent queue and an undefined number of FIFO queues. FIFO queues can be used in order to ensure the execution order of Blocks, when there are dependencies between them. That way, a thread can take for execution the first Block in the concurrent queue that still has been taken, and the first block introduced in any of the FIFO queues as long there is no thread executing the previous Block before it. This increases the probability for a thread to find work to do, and the source of work can be any part of the code. Again, we are not taking advantage of this feature in our code, but we can if we integrate it with a visualization interface in an Apple machine.

Finally, GCD allows to reduce TMO (consider block enqueueing as TMO), by allowing blocks to enqueue other blocks. That way it is possible to parallelize block enqueueing, so to balance this task across threads, instead of giving the task only to the main thread. The more cores used, the more interesting this option becomes.

As a summary we can see, following the GCD specification and our discussion, that the codes (with unbalanced work) that use it do better scale with CPU core increments than free OpenMP implementations.

### 2.3.4 Conclussions

With all this information we can intuitively see which algorithm overheads we should try to minimize, for a specific hardware. An experienced parallel programmer may already mentally do that procedure, but we didn't find any literature explaining a generic methodology for avoiding redundant and useless work, when programming parallel systems.

## Chapter 3

## Classification problem

## 3.1 Introduction

In volume visualization, the definition of the regions of interest is inherently an iterative trial-and-error process finding out the best parameters to classify and render the final image. Generally, the user requires a lot of expertise to analyze and edit these parameters through multi-dimensional transfer functions. There are paid manual classification services that give good results, but are not available to any one due to the cost of the service. Additionally, the time required for having the volumes classified usually is several weeks. Additionally, classification techniques applied to large volumes are usually computational intensive tasks, that require overnight computation and make the whole user-system interaction slow. So there is not a tool where the users of CT or MRI machines can easily and accurately visualize the results in real time.

We want to create a framework that defines the steps to be performed, and on each step or functionality, the methods implemented can be varied and changed. But there are fixed constraints, as the interactivity feature and a minimum of classification accuracy that must be satisfied.

FIGURE 3.1: Overview of the ECOC-based visualization framework.

In this work we want to implement supervised multi-classification techniques, that can generate classifiers using a small labeled subset of the volume to be classified. The idea is to create a software that allows to create a tool for the CT/MRI user (a doctor) to be able to interact with the volume generated, by labeling few points that the doctor will be sure about, and the rest will be classified automatically in real time.

For the interactivity constraint, we consider parallelism as the conceptual computing tool in which to rely for execution time performance. Given the data-parallelism nature of the data to be processed, we will explore several parallel computing systems (hardware+language) and select classification techniques that can offer different work division granularities to better exploit any possible parallel architecture available to us.

## 3.2 Visualization

Knowledge expressiveness of scientific data is one of the most important visualization goals. The abstraction process the final user should carry out in order to convey relevant information in the underlying data is normally a difficult task. User has to mentally process a large amount of data contained in several hundreds of slices to find features, boundaries between different structures, regions surrounding pathological areas, semantic structures, and so on. During the last few decades new means of outlining significant features are being developed to gather visual information contained in the data, such as ghost views, Focus+Context approaches [APT08], importance-driven visualizations and automatic viewpoint selections. Some of these methods [VKG05] [KSW06] are useful for the exploration of pre-classified data sets as well as non-classified ones. However, most of them [BHW\*07, KBKG08] require to previously define the structures of interest.

In volume rendering literature, many papers addressed classification by directly associating optical and importance properties to the different data values considering their belonging to a particular structure [PLB\*01]. Most of them are based on the edition of transfer functions (TF) [BPS97, KD98]. One-dimensional TFs only take into account scalar voxel values, but in some cases they could fail at accurately detecting complex combinations of material boundaries. Multi-dimensional TFs consider vectorial values or combinations of local measures of scalar values (e.g. position, statistical signatures, or derivatives [KD98]). However, the design complexity and the memory requirements increase with the TFs dimensionality. In general, the user coherently assigns similar optical properties to data values corresponding to the same region. Selection of regions or structures is indirectly defined by assigning to zero the opacity since totally transparent samples do not contribute to the final image. Then, the manual TF's definition even by skilled users becomes complicated. In this sense, many works have focused on developing user friendly interfaces that make this definition more intuitive. Special emphasis has been done in the design of interfaces that deal with the definition of a TF or partially automatize it [TM04, KKH01, MAB\*97]. Nevertheless, to recognize semantic structures that apply to identify additional semantic information requires more sophisticated techniques.

### **3.3** Classification techniques

Automatic and user-guided segmentation strategies based on image processing are used to obtain classified data sets. Recently, some preliminary works using learning methods have been published based on data driven and on image-driven classification. These classification methods provide users with a high level of information about data distribution and about the final visualization. Supervised methods such as bayesian networks, neural networks [TLM03], decision trees [FPT06] and non-supervised methods [TM04] have been applied in different user interfaces of volume applications. For instance, in [GMK\*92], clustering-based supervised and non-supervised learning methods are compared for classifying magnetic resonance data. An integration of interactive visual analysis and machine learning is used in an intelligent interface to explore huge data sets in [FWG09]. Still, the data driven classification problem as a pattern recognition process is an open issue that has been treated from different points of view: template matching, statistical, syntactic or structural, and neural [JDM00]. For instance, supervised statistical learning deals with the classification task by modeling the conditional probability distribution of the different pre-labelled data sample features.

Different Machine Learning (ML) approaches have been recently implemented using GPGPU for binary classifications in image processing applications. Clustering strategies and the computation of a k-nearest neighbor similarity classifier is presented in [GDB08]. A Geometrical Support Vector Machine classifier has also been implemented using GPGPU [HWS10]. It extends different GPGPU implementations for Neural Networks [YSMR10]. Adaboost is also a widely applied classifier. Based on a *weak classifier*, Adaboost defines an additive model combining simple weak classifiers to define a strong binary classifier with high generalization capability. Given its inherent parallel structure, its high performance, and its simplicity in order to train –Adaboost does not require tuning classifier parameters, Adaboost has a high potential for GPU applications.

Most of the previous approaches are binary by definition –they only learn to split from two possible labels<sup>1</sup>. In order to deal with multi-class labelling, they need to be combined in some way, for example, by means of a voting or a committee process. In this scope, the Error-Correcting Output Codes (ECOC) is widely applied as a general framework in the ML community in order to deal with multi-class categorization problems. The ECOC framework allows to combine any kind of classifiers, improving classification accuracy by correcting errors caused by the bias and the variance of the learning algorithm [DK95].

<sup>&</sup>lt;sup>1</sup>Note that we use the terms classification and labelling indistinctly to refer the assignment of labels to data samples.

### 3.4 Proposal

Our automatic volume labeling system bases on the combination of a set of trained binary classifiers. We consider the general ECOC framework to deal with multi-class labeling. As a case study, we use Adaboost to train the sets of binary classifiers. Next, we briefly review these two methodologies.

### 3.4.1 Error-Correcting Output Codes

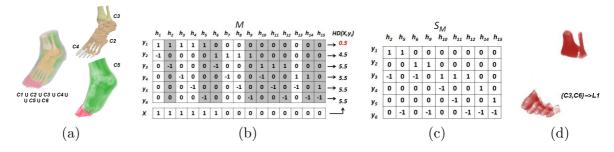

Given a set of N classes (volume structures or regions with certain properties) to be learnt in an ECOC framework, n different bi-partitions (groups of classes) are formed, and n binary problems over the partitions are trained. As a result, a codeword of length nis obtained for each class, where each position (bit) of the code corresponds to a response of a given classifier h (coded by +1 or -1 according to their class set membership, or 0 if a particular class is not considered for a given classifier). Arranging the codewords as rows of a matrix, we define a *coding matrix* M, where  $M \in \{-1, 0, +1\}^{N \times n}$ . Fig. 3.2(a) and (b) show a volume data set example and a coding matrix M, respectively. The matrix is coded using 15 classifiers  $\{h_1, ..., h_{15}\}$  trained using a few voxel samples for each class of a 6-class problem  $\{c_1, ..., c_6\}$  of respective codewords  $\{y_1, ..., y_6\}$ . The classifiers h are trained by considering the pre-labelled training data samples  $\{(\rho_1, l(\rho_1)), ..., (\rho_k, l(\rho_k))\}$ for a set of k data samples (voxels in our case), where  $\rho$  is a data sample and  $l(\rho_k)$  its label. For example, the first classifier  $h_1$  is trained to discriminate  $c_1$  against  $c_2$ , without taking into account the rest of classes. Some standard coding designs are one-versus-all, one-versus-one, and random [ASS02]. Mainly, they differ on the definition of the subgroups of classes in the partitions of each binary problem. Due to the huge number of bits involved in the traditional coding strategies, new problem-dependent designs have been proposed  $[ETP^*08]$ . These strategies take into account the distribution of the data in order to define the partitions of classes of the coding matrix M.

During the decoding or testing process, applying the *n* binary classifiers, a code *X* is obtained for each data sample  $\rho$  in the test set. This code is compared to the base codewords  $(y_i, i \in [1, ..., N])$  of each class defined in the matrix *M*, and the data sample is assigned to the class with the *closest* codeword (e.g. in terms of distance). In fig. 3.2(b), the new code *X* is compared to the class codewords  $\{y_1, ..., y_6\}$  using the Hamming Decoding [ASS02],  $HD(X, y_i) = \sum_{j=1}^n (1 - \operatorname{sign}(x^j \cdot y_i^j))/2$ , where  $X^j$  corresponds to the *j*-th value of codeword *X*, and the test sample is classified by class  $c_1$  with a measure of 0.5. The decoding strategies most widely applied are Hamming and Euclidean [ASS02], though other decoding designs have been proposed [EPR10].

### 3.4.2 Adaboost classifier

In this work, we train the ECOC binary classifiers h using Adaboost classifier. Adaboost is one of the main preferred binary classifiers in the ML community based on the concept of Boosting [FHT98]. Given a set of k training samples, we define  $h_i \sim F_i(\rho) = \sum_{m=1}^{\mathcal{M}} c_m f_m(\rho)$ , where each  $f_m(\rho)$  is a classifier producing values  $\pm 1$  and  $c_m$  are constants; the corresponding classifier is sign( $F(\rho)$ ). The Adaboost procedure trains the classifiers  $f_m(\rho)$  on weighed versions of the training sample, giving higher weights to cases that are currently misclassified [FHT98]. Then, the classifier is defined to be a linear combination of the classifiers from each stage. The binary Discrete Adaboost algorithm used in this work is shown in Algorithm 3.  $E_w$  represents expectation over the training data with weights  $w = (w_1, w_2, ..., w_k)$ , and  $1_{(S)}$  is the indicator of the set S (1 or 0 if S is or not satisfied). Finally, Algorithm 2 shows the testing of the final decision function  $F(\rho) = \sum_{m=1}^{\mathcal{M}} c_m f_m(\rho)$  using Adaboost with Decision Stump "weak classifier". A Decision Stump is a simple directional threshold over a particular feature value. Each Decision Stump  $f_m$  fits a threshold value  $T_m$  and a polarity (directionaly over the threshold)  $P_m$  over the selected *m*-th feature. In testing time,  $\rho^m$  corresponds to the value of the feature selected by  $f_m(\rho)$  on a test sample  $\rho$ . Note that  $c_m$  value is subtracted from  $F(\rho)$  if the classifier  $f_m(\rho)$  is not satisfied on the test sample. Otherwise, positive values of  $c_m$  are accumulated. Finally decision on  $\rho$  is obtained by sign $(F(\rho))$ .

#### ALGORITHM 1: Discrete Adaboost training algorithm.

- 1: Start with weights  $w_i = 1/k, i = 1, ..., k$ .

- 2: Repeat for m = 1, 2, .., (M):

- (a) Fit the classifier  $f_m(\rho) \in -1, 1$  using weights  $w_i$  on the training data.

- (b) Compute  $\operatorname{err}_m = E_w[1_{(l(\rho) \neq fm_{(\rho)}]}], c_m = \log((1 \operatorname{err}_m)/\operatorname{err}_m).$

- (c) Set  $w_i \leftarrow w_i \exp[c_m \cdot 1_{(l(\rho_i) \neq fm_{(\rho_i)})}], i = 1, 2, ..., k$ , and normalize so that  $\sum_i w_i = 1$ .

- 3: Output the classifier  $F(\rho) = \operatorname{sign}[\sum_{m=1}^{\mathcal{M}} c_m f_m(\rho)].$

#### ALGORITHM 2: Discrete Adaboost testing algorithm.

- 1: Given a test sample  $\rho$

- 2:  $F(\rho) = 0$

- 3: Repeat for m = 1, 2, .., M:

- (a)  $F(\rho) = F(\rho) + c_m (P_m \cdot \rho^m < P_m \cdot T_m);$

```

4: Output \operatorname{sign}(F(\rho))

```

## 3.5 Proposal: General framework for multi-class volume labeling

Here, we present our automatic system for multi-class volume labeling. The system performs the following stages: a) All-pairs ECOC multi-class learning, b) ECOC submatrix definition, c) Adaptive decoding, and d) Label mapping.

### 3.5.1 All-pairs multi-class learning

Given a set of pre-labelled samples for each volume structure, we choose the one-versusone ECOC design of N(N-1)/2 classifiers to train the set of all possible pairs of labels. An example of a one-versus-one ECOC coding matrix for a 6-class foot problem is shown in Fig. 3.2(a) and (b). The positions of the coding matrix M coded by +1 are considered as one class for its respective classifier  $h_j$ , and the positions coded by -1 are considered as the other one. For example, the first classifier is trained to discriminate  $c_1$  against  $c_2$ ; the second one classifies  $c_1$  against  $c_3$ , etc., as follows:

$$h_1(x) = \begin{cases} 1 & \text{if } X \in \{c_1\} \\ -1 & \text{if } X \in \{c_2\} \end{cases}, ..., \quad h_{15}(x) = \begin{cases} 1 & \text{if } X \in \{c_5\} \\ -1 & \text{if } X \in \{c_6\} \end{cases}$$

(3.1)

FIGURE 3.2: (a) True labels for a foot volume of six classes; (b) One-versus-one ECOC coding matrix M for the 6-class problem. An input test codeword X is classified by class  $c_1$  using the Hamming Decoding; (c) Submatrix  $S_M$  defined for an interaction set  $I = \{\{c_1, c_2, c_4, c_5\}, \{c_3, c_6\}\};$  (d) Visualization in the new label space.

The selection of the one-versus-one design has two main benefits for our purpose. First, though all pairs of labels have to be split in a one-versus-one ECOC design, the individual problems that we need to train are significantly smaller compared to other classical ECOC classifiers (such as one-versus-all). As a consequence, the problems to be learnt are usually easier since the classes have less overlap. Second, as shown in Fig. 3.2, considering binary problems that split individual labels allow us for combining groups of labels on-demand just by the selection of a subgroup of previouly trained classifiers, as we show next.

### 3.5.2 ECOC submatrix definition

Given a volume that can be decomposed into N different possible labels, we want to visualize in rendering time the set of labels requested by the user. For this purpose, we use a small set of ground truth voxels described using spatial, value, and derivative features to train the set of N(N-1)/2 Adaboost binary problems that defines the oneversus-one ECOC coding matrix M of size  $N \times n$ . Then, let us define the interaction of the user as the set  $I = \{I_0, .., I_z\} = \{\{c_i, .., c_j\}, ..\{c_k, .., c_l\}\}$ , where  $I, |I| \in \{1, .., N\}$ is the set of groups of labels selected by the user, and  $I_0$  contains the background (always referred as  $c_1$ ) plus the rest of classes not selected for rendering,  $I_0 = \{c_i\}, \forall c_i \notin \{I_1, .., I_z\}, \bigcup_{c_i \in I} = \{c_1, .., c_N\}, \bigcap_{c_i \in I} = \emptyset$ . Then, the submatrix  $S_M \in \{-1, 0, +1\}^{N \times Z}$ is defined, where  $Z \leq n$  is the number of classifiers selected from M that satisfies the following constraint,

$$h_i | \exists j, M_{ji} \in \{-1, 1\}, c_j \in I \setminus I_0$$

(3.2)

For instance, in a 6-class problem of 15 one-versus-one ECOC classifiers (see Fig. 3.2(b)), the user defines the interaction  $\{c_3, c_6\}$ , resulting in the interaction model  $I = \{\{c_1, c_2, c_4, c_5\}, \{c_3, c_6\}\}$ in order to visualize two different labels, one for background and other one for those voxels with label  $c_3$  or  $c_6$ . Then, from the original matrix  $M \in \{-1, 0, +1\}^{6 \times 15}$ , the submatrix  $S_M \in \{-1, 0, +1\}^{6 \times 9}$  is defined, as shown in Fig. 3.2(c). Note that the identifier i of each classifier  $h_i$  in  $S_M$  refers to its original location in M.

### 3.5.3 Adaptive decoding

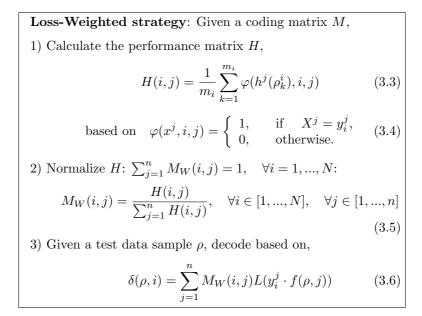

The proposed ECOC submatrix  $S_M$  encodes the minimum required number of binary classifiers from a one-versus-one coding matrix M to label the sets of structures defined by the user in I. However, this novel definition of ECOC submatrices requires a readjustment of the decoding function  $\delta$  applied. For instance, if we look at the matrix M of Fig. 3.2(b), one can see that each row (codeword) of M contains the same number of positions coded by zero. If one applies a classical Hamming decoding, obviously a bias in the comparison with a test and a matrix codeword is introduced to those positions comparing membership  $\{-1, 1\}$  to 0. Note that the zero value means that the class has not been considered, and thus, it makes no sense to include a decoding value for those positions. However, since in the one-versus-one design all the codewords contain the same number of zeros, the bias error introduced for each class is the same, and thus, the decoding measurements using classical decoding functions are comparable. In our case, this constraint does not hold. Look at the submatrix  $S_M$  of Fig. 3.2(c). The selection of submatrices often defines coding matrices with different number of positions coded to zero for different codewords. In order to be able to successfully decode a submatrix  $S_M$  we take benefit from the recent Loss-Weighted proposal [EPR10], which allows the decoding of ternary ECOC matrices avoiding the error bias introduced by the different number of codeword positions coded by zero. The Loss-Weighted decoding is defined as a combination of normalized probabilities that weights the decoding process. We define a weight matrix  $M_W$  by assigning to each position of the codeword codified by  $\{-1, +1\}$ a weight of  $\frac{1}{n-z}$ , being z the number of positions of the codeword coded by zero. Moreover, we assign a weight of zero to those positions of the weight matrix  $M_W$  that contain a zero in the coding matrix M. In this way,  $\sum_{j=1}^{n} M_W(i,j) = 1, \forall i = 1, ..., N$ . We assign to each position (i, j) of a performance matrix H a continuous value that corresponds to the performance of the classifier  $h_j$  classifying the samples of class  $c_i$  as shown in eq. 3.3. Note that this equation makes H to have zero probability at those positions corresponding to unconsidered classes. Then, we normalize each row of the matrix Hso that  $M_W$  can be considered as a discrete probability density function (eq. 3.5). In fig. 3.3, a weight matrix  $M_W$  for a 3-class toy problem of four classifiers is estimated. Fig. 3.3(a) shows the coding matrix M. The matrix H of Fig. 3.3(b) represents the accuracy of the classifiers testing the instances of the training set. The normalization of Hresults in a weight matrix  $M_W$  shown in Fig. 3.3(c). Once we compute the weight matrix  $M_W$ , we include this matrix in a loss-function decoding formulation,  $L(\theta) = \mathbf{e}^{-\theta}$ , where  $\theta$  corresponds to  $y_i^j \cdot f(\rho, j)$ , weighted using  $M_W$ , as shown in eq. 3.6. The summarized algorithm is shown in table 3.1.

TABLE 3.1: Loss-Weighted algorithm.

### 3.5.4 Adaboost Look up table (LUT) representation

We propose to define a new and equivalent representation of  $c_m$  and  $|\rho|$  that facilitate the parallelization of the testing. We define the matrix  $V_{f_m(\rho)}$  of size  $3 \times (|\rho| \cdot M)$ , where  $|\rho|$  corresponds to the dimensionality of the feature space. First row of  $V_{f_m(\rho)}$ codifies the values  $c_m$  for the corresponding features that have been considered during training. In this sense, each position i of the first row of  $V_{f_m(\rho)}$  contains the value  $c_m$ for the feature  $mod(i, |\rho|)$  if  $mod(i, |\rho|) \neq 0$  or  $|\rho|$ , otherwise. The next value of  $c_m$ for that feature is found in position  $i + |\rho|$ . The positions corresponding to features not considered during training are set to zero. The second and third rows of  $V_{f_m(\rho)}$ for column i contains the values of  $P_m$  and  $T_m$  for the corresponding Decision Stump. Note that in the representation of  $V_{f_m(\rho)}$  we lose the information of the order in which the Decision Stumps were fitted during the training step. However, though in different order, all trained "weak classifiers" are represented, and thus, the final additive decision model  $F(\rho)$  is equivalent. In our proposal, each "weak classifier" is codified in a channel of a 1D-Texture.

### 3.5.5 Label mapping

Given the submatrix  $S_M$  and the user interaction model I, after classification of a voxel  $\rho$  applying the Loss-Weighted decoding function, the obtained classification label  $c_i, i \in \{1, ..N\}$  is relabelled applying the mapping,

$$L_M(I, c_i) = \begin{cases} l_1 & \text{if } c_i \in I_1 \\ \dots & \\ l_z & \text{if } c_i \in I_z \end{cases}$$

where  $l_i, i \in \{1, ..., z\}$  allows to assign RGB $\alpha$  or importance values to all voxels that belong to the corresponding selected classes in  $I_i$ . These functions are useful to provide flexibility to our framework in order to be applied in several visualization tasks, such as importance-driven visualizations or automatic viewpoint selections. As an example, applying the interaction model  $I = \{\{c_1, c_2, c_4, c_5\}, \{c_3, c_6\}\}$  for the 6-class problem of Fig. 3.2(a), we obtain the submatrix  $S_M$  of Fig. 3.2(c). Applying the Loss-Weighted decoding over  $S_W$ , and the mapping function  $\{\{c_1, c_2, c_4, c_5\}, \{c_3, c_6\}\} \rightarrow \{0, 1\}$ , the new volume representation is shown n Fig. 3.2(d).

$$M = \begin{bmatrix} 1 & 1 & -1 & 0 \\ 1 & -1 & 0 & 0 \\ -1 & 1 & 1 & -1 \end{bmatrix} \quad H = \begin{bmatrix} 0.955 & 0.955 & 1.000 & 0.000 \\ 0.900 & 0.800 & 0.000 & 0.000 \\ 1.000 & 0.905 & 0.805 & 0.805 \end{bmatrix} \quad M_W = \begin{bmatrix} 0.328 & 0.328 & 0.344 & 0.000 \\ 0.529 & 0.471 & 0.000 & 0.000 \\ 0.285 & 0.257 & 0.229 & 0.229 \end{bmatrix}$$

(a) (b) (c)

FIGURE 3.3: (a) Coding matrix of four classifiers for a 3-class toy problem, (b) Performance matrix, and (c) Weight matrix.

### **3.6** Classification parallelization implementation

### 3.6.1 Introduction

In this section, we will explain in detail which part of the framework we have parallelized and how we have done it. We will describe some possible parallelizations and select one following the AIMparallel methodology. Additionally we will implement one of the discarded implementations to compare the results and verify.

The slowest part on the framework is the classification, where depending on the number of classes and voxels on the volume, can last about 5 hours on Matlab. For that reason, on this thesis we parallelized the classification step of the framework, where many binary Adaboost classifiers are combined using an ECOC matrix, for obtaining labels from more than two clases for each boxel.

#### 3.6.2 Algorithm overview

In this section we describe the algorithm being parallelized, and the tasks it can be decomposed into.

As shown in Algorithm 3, the critical section in our application is a triple iteration loop to go through all voxels of the voxel model, VM, in an ordered traversal. Each iteration performs three tasks: the gradient computation (Task 1), the X code word estimation (Task 2), and the final labeling calculation (Task 3). These tasks are called T1, T2 and T3, respectively in Algorithm 3, and are performed for each voxel  $v_{xyz}$ .

| ALGORITHM 3: Critical section serial pseudocode for the testing stage.            |                                                                         |

|-----------------------------------------------------------------------------------|-------------------------------------------------------------------------|

| inputVolume                                                                       | : Original 3D voxel model with density values $(d)$                     |

| outputVolume                                                                      | : Multiclass labeled voxel model with single value samples              |

| voxelFeatures                                                                     | : pointer to the 8 sample features for the voxel sample being processed |

| $\mathcal{L}$                                                                     | : $\mathcal{L}$ matrix pointer containing the LUTs                      |

| X                                                                                 | : code word of binary decission values for a single voxel sample        |

| $\mathbf{M}$                                                                      | : coding matrix                                                         |

| background_valu                                                                   | ie: density value threshold for the actual voxel sample to be processed |

| for $z \leftarrow 0$ to $dim_z$ do                                                |                                                                         |

| for $y \leftarrow 0$ to $dim_y$ do                                                |                                                                         |

| for $x \leftarrow 0$ to $dim_x$ do                                                |                                                                         |

| $d \leftarrow input[z][y][x] // d$ refers to the density value in the voxel model |                                                                         |

| if $d > background\_value$ then                                                   |                                                                         |

| computeGradient(z, y, x, inputVolume[z][y][x], voxelFeatures); // T1              |                                                                         |

| XCodeEstimation(voxelFeatures, $\mathcal{L}$ , X); // T2                          |                                                                         |

| Fin                                                                               | $\operatorname{halLabeling}(X, M, outputVolume[z][y][x]); // T3$        |

| end                                                                               |                                                                         |

| end                                                                               |                                                                         |

| end                                                                               |                                                                         |

| $\mathbf{end}$                                                                    |                                                                         |

Specifically, the features of each  $v_{xyz}$  are computed and stored in memory (pointed by the voxelFeatures variable), at each iteration in the *computeGradient* function (T1). Then, at the same iteration, a X code word of binary decision values is generated by XCodeEstimation function (T2) for the actual  $v_{xyz}$  voxel. In this function, the *voxelFeatures* and the  $\mathcal{L}$  variables are read to generate the contents of X. In order to improve serial execution, we modified the Discrete Adaboost testing algorithm (see Algorithm 2). The features are computed depending on the  $P_m$  values (lines 3(a) - 3(b)), but the Adaboost Look Up Table allows to compute all the features without branching depending on the weight. Then we are substituting conditional statements by more efficient arithmetical and logical operations. So, in our algorithm, lines 3(a) and 3(b) are substituted by Equation 3.7.

$$F(\rho) = F(\rho) + c_m \cdot ((2 \cdot (P_m \cdot \rho^m < P_m \cdot T_m)) - 1)$$

(3.7)

Finally, before changing to the next voxel, the *FinalLabeling* function (T3) reads X and the coding matrix, M, to generate a single class value for  $v_{xuz}$ .

### 3.6.3 Generic parallelization proposals

In this section, we follow the methodology described in the theoretical environment we defined, for each one of the tasks involved in the Discrete Adaboost testing algorithm (see Section 3.6.2). At the end of the section, we comment the overheads for the interactions between tasks (T1, T2 and T3).

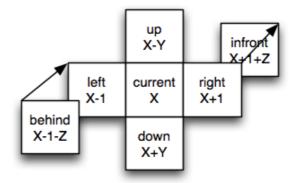

#### 3.6.3.1 Task 1 and high level overheads mapping

First we analyze the parallelization possibilities for Task 1 (T1), which is devoted to the stencil gradient calculation, as we can see on Figure 3.4. In this task, the gradients  $g_x$ ,  $g_y$  and  $g_z$  of a sampled voxel  $v_{xyz}$ , as well as its magnitude |g|, are computed using central differences. T1 is a 7 point stencil operation. Thus, for each dimension, we need the two neighbor voxel values of  $v_{xyz}$ . This operation is data independent among voxel samples, because the source data is not modified, and the results are 8 output-only values per voxel.

FIGURE 3.4: Stencil operation used on T1. The neighbors indicated are used for generating extra feature values of X.

As a first parallelization option  $T1_1$  we could use a thread for each voxel and calculate the gradients for all of them concurrently. This generates TMO but less than having three threads per voxel, that in addition to more TMO, they would generate TCO and WPO on the reduction operations.

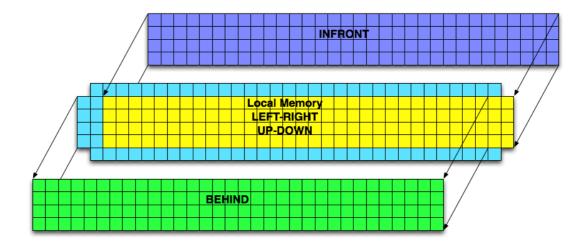

FIGURE 3.5:  $T1_1$  implementation. On yellow the voxels for which we are calculating the gradients. Infront and behind are stored on private memory, and yellow and blue on local memory. The image corresponds to the data used by a workgroup of  $32 \times 4$  work items.

As  $T1_2$  option we can then focus on data locality to reduce TCO. The only way to do so is by making threads to process more than one voxel, specifically voxels that share data for calculating the gradients. This reduces the number of threads, therefore it produces WPO but also reduces TMO and TCO. We can find in the literature several methods for reducing TCO in this way like the Semi-stencil algorithm [dlCAPC10] that exploits data locality. In our case, as we are using only one value per neighboring side, and we are not using the central value, we can only do operations for the voxel corresponding to the central value. Thus this technique is not useful. Depending on the architecture we will calibrate the number of threads taking into account this analysis.

#### 3.6.3.2 Task 2 and high level overheads mapping

Next, we propose several parallelization options for Task 2 (T2), which performs the binary-classification step. T2 refers to the testing or decoding process, where the corresponding LUTs of the n binary classifiers are applied to each voxel  $v_{xyz}$  (see Section 3.4.1).

As we defined in Section 3.5.4, each  $\mathcal{L}$  has three  $(|\rho| \times W_c)$ -sized rows. Let dim(VM) be the total amount of voxels of the model. Thus, the T2 cost is  $O(dim(VM) \times n \times (|\rho| \times W_c))$ . We propose multiple options for parallelizing T2:

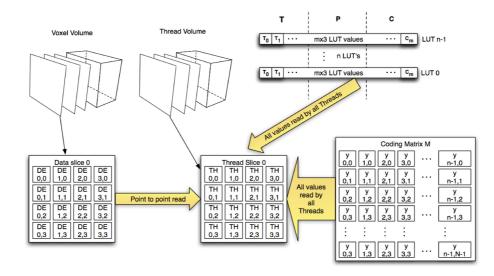

• First one is called  $T2_1$  and it consists of creating a thread for each voxel  $v_{xyz}$ , as shown in Fig. 3.6. Ideally, in a machine with dim(VM) processors, the final cost of this option is  $O(n \times (|\rho| \times W_c))$ . Among the three values dim(VM) will always

be greater than n or  $(|\rho| \times W_c)$ . Also, there is no thread to thread communication so we have a balance between parallelism (WPO) and communication (TCO), and also thread management (TMO).

FIGURE 3.6: Parallelization option  $T2_1$ : a thread is created for each voxel  $v_{xyz}$ .

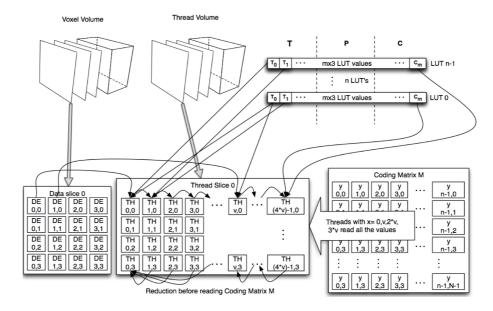

•  $T2_2$  is a second parallelization option of Task 2. In this option we increase parallelism, as shown in Fig. 3.7. We can create  $dim(VM) \times |\rho| \times W_c$ ) threads. One thread computes a value for each LUT-entry for each voxel (see Fig. 3.7). The theoretical cost of this approach is O(n). However, threads that classify the same voxel  $v_{xyz}$  should communicate in order to compute the final sign  $sign(F(\rho))$  for  $v_{xyz}$ . This behavior increases the thread communication overhead TCO defined in Section 2.3.2. Moreover, this option also has WPO and TMO because there are different numbers of threads being used on each step of T2. So the increased parallelism is only effective in some steps of  $T2_2$ .

FIGURE 3.7: Parallelization option  $T2_2$ : one thread computes a single LUT value for each LUT, for a single voxel. Some extra communication among threads should be done in order to compute the final  $sign(F(\rho))$  for each  $v_{xyz}$ .

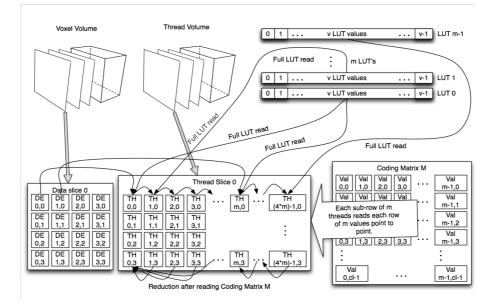

• Finally,  $T2_3$  is the last parallelization option we propose for Task 2. It is based on creating  $n \times \dim(VM)$  threads. Each thread processes one voxel  $v_{xyz}$  with one LUT. Then, the final cost is  $O(|\rho| \times W_c)$ . In this solution, we deal with  $\dim(VM)$ groups of n threads with a value related to the same voxel  $v_{xyz}$ . These n threads can use this own generated values (ideally stored on local memories) to process later T3 in parallel. This option still presents a big TCO because all the threads need the data generated on T1 but it is possible to skip the final reduction step, depending on the configuration of step T3. It has more WPO but less TCO than  $T2_2$ .

FIGURE 3.8: Parallelization option  $T2_3$ : one thread reads a full LUT, and a row of m threads share the same value from the input data. Reading of the coding matrix M is done concurrently.